The Qualcomm Computex 2024 Keynote Live Blog (10:30pm PT/05:30 UTC)

Published: Jun 3nd 2024 1:10am on AnandTech

For our second keynote of the day for Computex, we have the 4th Musketeer of the great PC powers, Qualcomm. Slated to be the most PC-focused of the four keynotes, company CEO Cristiano Amon will be presenting a keynote entitled “The PC Reborn.” And while Amon is no stranger to giving keynotes, this is slated to be his most PC-centric keynote yet, giving Computex attendees a clearer idea of how focused Qualcomm will be on the PC market with their new Windows-on-Arm SoCs.

The big focus for today's keynote is expected to be the Snapdragon X Elite and X Plus SoCs, which Qualcomm announced over half a year ago, and has been touting ever since. Now, the first consumer devices based on these chips are just a couple of weeks away from shipping, so Qualcomm is in their final promotional push for their new Windows-on-Arm platform. As a result, Qualcomm should have a lot more hardware to show off, with final silicon and shipping SKUs already defined.

While Snapdragon X is not Qualcomm’s first effort to ship an Arm-based SoC for Windows devices – there are 3 generations of 8cx Gen 3 platforms that everyone is happy never to mention again – the Snapdragon X is Qualcomm’s most serious effort yet. At its core is the new, high-performance/high-efficiency Oryon CPU core, which combined with the rest of Qualcomm’s tried-and-true mobile hardware experience, the company is hoping to mold into a revolutionary Arm-based SoC for Windows laptops. The company is also counting on a decade of software development on Microsoft’s part to make the Windows-on-Arm ecosystem whole, not to mention as frictionless as possible.

Besides energy efficiency, Qualcomm’s other big push is on the burgeoning field of NPUs. The Snapdragon X NPU is rated to deliver 45 TOPS of INT8 performance, which makes it the first PC NPU to meet Microsoft’s hardware requirement for Windows 11 Copilot+ AI functionality. So Qualcomm is looking to leverage this time-limited opportunity to be the first to offer new functionality in the Windows space – a privilege normally reserved for Intel or AMD.

Come join us at 9:30pm PT / 12:30am ET / 05:30 UTC to get all the details.

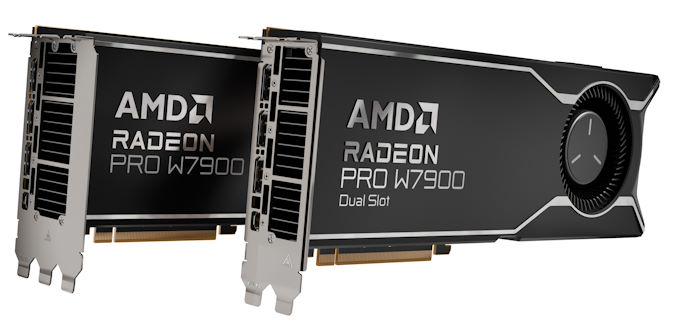

AMD Slims Down Compute With Radeon Pro W7900 Dual Slot For AI Inference

Published: Jun 2nd 2024 11:05am on AnandTech

While the bulk of AMD’s Computex presentation was on CPUs and their Instinct lineup of dedicated AI accelerators, the company also has a small product refresh for the professional graphics and workstation AI crowd. AMD is releasing a dual-slot version of their high-end Radeon Pro W7900 card – aptly named the W7900 Dual Slot – with the intent being to improve compute density in workstations by making it possible to install 4 of the cards inside a single chassis.

The release of a dual-slot version of the card comes after the original Radeon Pro W7900 was the first time AMD went with a larger, triple-slot form factor for their flagship workstation card. With the W7000 generation bringing an all-around increase in power consumption, pushing the W7900 to 295 Watts, AMD originally opted to release a larger card for improved acoustics. However this came at the cost of compute density, as most systems could only fit 2 of the thicker cards. As a result, AMD is opting to release a dual-slot version of the hardware as well, to offer a more competitive product for high-density workstation systems – particularly those doing local AI inference.

AMD Radeon Pro Specification Comparison AMD Radeon Pro W7900DS AMD Radeon Pro W7900 AMD Radeon Pro W7800 AMD Radeon Pro W6800 ALUs 12288 (96 CUs) 8960 (70 CUs) 3840 (60 CUs) ROPs 192 128 96 Boost Clock 2.495GHz 2.495GHz 2.32HHz Peak Throughput (FP32) 61.3 TFLOPS 45.2 TFLOPS 17.8 TFLOPS Memory Clock 18 Gbps GDDR6 18 Gbps GDDR6 16 Gbps GDDR6 Memory Bus Width 384-bit 256-bit 256-bit Memiry Bandwidth 864GB/sec 576GB/sec 512GB/sec VRAM 48GB 32GB 32GB ECC Yes (DRAM) Yes (DRAM) Yes (DRAM) Infinity Cache 96MB 64MB 128MB Total Board Power 295W 260W 250W Manufacturing Process GCD: TSMC 5nm MCD: TSMC 6nm GCD: TSMC 5nm MCD: TSMC 6nm TSMC 7nm Architecture RDNA3 RDNA3 RDNA2 GPU Navi 31 Navi 31 Navi 21 Form Factor Dual Slot Blower Triple Slot Blower Dual Slot Blower Dual Slot Blower Launch Date 06/2024 Q2'2023 Q2'2023 06/2021 Launch Price (MSRP) $3499 $3999 $2499 $2249Other than the narrower cooler, the Radeon Pro W7900DS is for all intents and purposes identical to the original W7900, with the same Navi 31 GPU being driven to the same clockspeeds, and the overall board being run to the same 295 Total Board Power (TBP) limit. This is paired with the same 18Gbps GDDR6 as before, giving the card 48GB of VRAM.

Officially, AMD doesn’t have a noise specification for these cards. But you can expect that the W7900DS will be louder than its triple-slot senior. By all appearances, AMD is just using the cooler from the W7800, which was a dual-slot card from the start, so that cooler is being tasked with handling another 35W of heat dissipation.

As the W7800 was also AMD’s fastest dual-slot card up until now, it’s an apt point of comparison for compute density. With its full-fat Navi 31 GPU, the W7900DS will offer about 36% more compute/pixel throughput than its sibling/predecessor. So it’s a not-insubstantial improvement for the very specific niche AMD has in mind for the card.

And like so many other things being announced at Computex this year, that niche is AI. While AMD offers PCIe versions of their Instinct MI210 accelerators, those cards are geared at servers, with fully-passive coolers to match. So workstation-level compute is largely picked up by AMD’s Radeon Pro workstation cards, which are intended to go into a traditional PC chassis and use active cooling (blowers). In this case, AMD is specifically going after local inference workloads, as that’s what the Radeon hardware and its significant VRAM pool are best suited for.

The Radeon Pro W7900 Dual Slot will drop on June 19th. Notably, AMD is introducing the card at a slightly lower price tag than they launched the original W7900 at last year, with the W7900DS hitting retail shelves at $3499, down from the W7900’s original $3999 price tag.

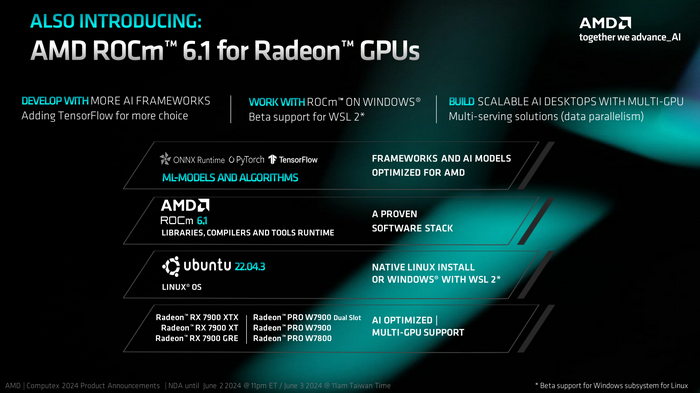

ROCm 6.1 For Radeons Coming as WellAlongside the release of the W7900DS, AMD is also promoting the upcoming Radeon release of ROCm 6.1, their software stack for GPU computing. While baseline ROCm 6.1 was introduced back in April, the Windows version of AMD’s software stack is still a trailing (and feature limited) release. So that is slated to finally get bumped up to a ROCm 6.1 release on June 19th, the same day the W7900DS launches.

ROCm 6.1 for Radeons is slated to bring a couple of major changes/improvements to the stack, particularly when it comes to expanding the scope of available features. Notably, AMD will finally be shipping Windows Subsystem for Linux 2 (WSL2) support, albeit at a beta level, allowing Windows users to access the much richer feature set and software ecosystem of ROCm under Linux. This release will also incorporate improved support for multi-GPU configurations, perfect timing for the launch of the Radeon Pro W7900DS.

Finally, ROCm 6.1 sees TensorFlow integrated into the ROCm software stack as a first-class citizen. While this matter involves more complexities than can be summarized in a simple news story, native TensorFlow support under Windows was previously blocked by a lack of a Windows version of AMD’s MIOpen machine learning library. Combined with WSL2 support, developers will have two ways to access TensorFlow on Windows systems going forward.

Gallery: AMD Radeon Pro W7900DS Press Deck

AMD Launching New CPUs for AM4: Ryzen 5000XT Series Coming in July

Published: Jun 2nd 2024 11:04am on AnandTech

During their opening keynote at Computex 2024, AMD announced their intention to launch a pair of new Ryzen 5000 processors for their legacy AM4 platform. The new chips, both getting the XT suffix, will be the Ryzen 9 5900XT, a 16 core Zen 3 part, while the Ryzen 7 5800XT will be an 8 core Zen 3.

The new chips are intended to underscore AMD's ongoing commitment to supporting their consumer platforms over several years. And while the specification changes are rather minor overall – the Zen 3 CPU architecture has long since been taken as far as it can reasonable go – it does give AMD a chance to refresh the platform by slinging hardware at new price points. AMD did something very similar for the Ryzen 3000 generation with the late-model Ryzen 3000 XT chips.

AMD Ryzen 5000XT Series Processors (Zen 3) AnandTech Cores / Threads Base Freq Turbo Freq L2 Cache L3 Cache TDP Ryzen 9 5950X 16C / 32T 3.4 GHz 4.9 GHz 8 MB 64 MB 105 W Ryzen 9 5900XT 16C / 32T TBC 4.8 GHz 8 MB 64 MB 105 W Ryzen 7 5800XT 12C / 24T TBC 4.8 GHz 6 MB 32 MB 105 W Ryzen 7 5800X 12C / 24T 3.8 GHz 4.7 GHz 6 MB 32 MB 105 WWe've dedicated many column inches covering Zen 3 and the Ryzen 5000 series since they launched in late 2020, so there isn't anything new to add here. Zen 3 is no longer AMD's latest and greatest, but the platform as a whole is quite cheap to produce, making it a viable budget offering for new builds, or offering one last upgrade for old builds.

The Ryzen 9 5900XT is a 16 core part, and isn't to be confused with the Ryzen 9 5900X, which is a 12 core part. It ships with a peak turbo clockspeed of 4.8GHz, 100 MHz lower than the top-tier Ryzen 9 5950X. This makes it's XT designation somewhat of a misnomer compared to previous generations of XT chips, although it's clear that AMD has boxed themselves into a corner with their naming scheme, as they both need a way to designate that this is a new chip, and yet still place it below the 5950X.

Looking at the second chip, we have the Ryzen 7 5800XT. This is an 8 core part that does improve on its predecessor, offering a 4.8GHz max turbo clock that is 100MHz higher than the Ryzen 7 5800X's. Both chips otherwise share the same characteristics, including 6 MB of L2 cache and 32 MB of L3 cache, and all four of the chips – including the two new XT series and the corresponding X series chips – all come with a 105 Watt TDP.

In terms of motherboard compatibility, all of the AM4 motherboards that currently support the Ryzen 5000 series are also compatible with the Ryzen 5000XT series, although users are likely to need to perform a firmware update to ensure maximum compatibility; they are the same chips, but the microcodes are likely different.

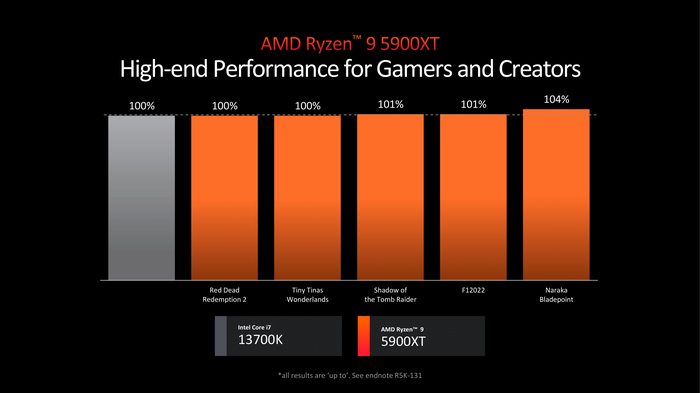

AMD has provided some gaming performance figures comparing the Ryzen 9 5900XT to Intel's 13th Gen Core i7-13700K. It does offer very modest yet marginal gains in games by up to 4%; it's not mind-blowing, but the price could be the decisive factor here.

Regarding price, AMD hasn't disclosed anything official yet ahead of the expected launch of the Ryzen 5000XT series chips in July. It's hard to make a case for a pair of chips to be considered a fully-fledged series, but it does open up the doors for AMD to perhaps launch more 5000XT series chips in the future.

AMD Plans Massive Memory Instinct MI325X for Q4'24, Lays Out Accelerator Roadmap to 2026

Published: Jun 2nd 2024 11:02am on AnandTech

In a packed presentation kicking off this year’s Computex trade show, AMD CEO Dr. Lisa Su spent plenty of time focusing on the subject of AI. And while the bulk of that focus was on AMD’s impending client products, the company is also currently enjoying the rapid growth of their Instinct lineup of accelerators, with the MI300 continuing to break sales projections and growth records quarter after quarter. It’s no surprise then that AMD is looking to move quickly then in the AI accelerator space, both to capitalize on the market opportunities amidst the current AI mania, as well as to stay competitive with the many chipmakers large and small who are also trying to stake a claim in the space.

To that end, as part of this evening’s announcements, AMD laid out their roadmap for their Instinct product lineup for both the short and long term, with new products and new architectures in development to carry AMD through 2026 and beyond.

On the product side of matters, AMD is announcing a new Instinct accelerator, the HBM3E-equiipped MI325X. Based on the same computational silicon as the company’s MI300X accelerator, the MI325X swaps out HBM3 memory for faster and denser HBM3E, allowing AMD to produce accelerators with up to 288GB of memory, and local memory bandwidths hitting 6TB/second.

Meanwhile, AMD also showcased their first new CDNA architecture/Instinct product roadmap in two years, laying out their plans through 2026. Over the next two years AMD will be moving very quickly indeed, launching two new CDNA architectures and associated Instinct products in 2025 and 2026, respectively. The CDNA 4-powered MI350 series will be released in 2025, and that will be followed up by the even more ambitious MI400 series in 2026, which will be based on the CDNA "Next" architecture.

AMD Unveils Ryzen 9000 CPUs For Desktop, Zen 5 Takes Center Stage at Computex 2024

Published: Jun 2nd 2024 11:00am on AnandTech

During AMD's Computex 2024 kick-off keynote, AMD's CEO, Dr. Lisa Su, officially unveiled and announced the company's next generation of Ryzen processors. Today marks the first unveiling of AMD's highly anticipated Zen 5 microarchitecture via the Ryzen 9000 series, which is set to bring several advancements over Zen 4 and the Ryzen 7000 series for desktop PCs, which will launch sometime in July 2024.

AMD has unveiled four new chip SKUs using its Zen 5 microarchitecture. The AMD Ryzen 9 9950X processor will be the new consumer flagship part, featuring 16 CPU cores and a speedy 5.7 GHz maximum boost frequency. The other SKUs include, 6, 8, and 12 core parts, giving users a varied combination of core and thread counts. All four of these initial chips will be X-series chips, meaning they will have an unlocked multipliers and higher TDPs/clockspeeds.

In regards to performance, AMD is touting an average (geomean) IPC increase in desktop workloads for Zen 5 of 16%. And with the new desktop Ryzen chips' turbo clockspeeds remaining largely identical to their Ryzen 7000 predecessors, this should translate into similar performance expectations for the new chips.

The AMD Ryzen 9000 series will also launch on the AM5 socket, which debuted with AMD's Ryzen 7000 series and marks AMD's commitment to socket/platform longevity. Along with the Ryzen 9000 series will come a pair of new high-performance chipsets: the X870E (Extreme) and the regular X870 chipsets. The fundamental features that vendors will integrate into their specific motherboards remain tight-lipped. Still, we do know that USB 4.0 ports are standard on the X870E/X870 boards, along with PCIe 5.0 for both PCIe graphics and NVMe storage, with higher AMD EXPO memory profile support expected than previous generations.

AMD Announces The Ryzen AI 300 Series For Mobile: Zen 5 With RDNA 3.5, and XDNA2 NPU With 50 TOPS

Published: Jun 2nd 2024 11:01am on AnandTech

During AMD's opening keynote at Computex 2024, company CEO Dr. Lisa Su revealed AMD's latest AI PC-focused chip lineup for the mobile market, the Ryzen AI 300 series. Based on AMD's new Zen 5 CPU microarchitecture, the Ryzen AI 300 series – codenamed Strix Point – is intended to offer an across-the-board improvement in mobile SoC performance, with AMD proclaiming that the Ryzen AI 300 series will offer the fastest AI inference performance within the compact and portable PC market.

Under the hood, the new mobile SoC from AMD incorporates not only their new Zen 5 CPU architecture, but also their new RDNA 3.5-based integrated graphics, and the third generation XDNA2-based NPU, the latter of which is rated to deliver 50 TOPS of performance for AI-based workloads. As a result, the Ryzen AI 300 series represents a significant upgrade in AMD's mobile chip lineup, with all of the major aspects of the platform receiving a major upgrade versus their Zen 4-era Phoenix/Hawk Point SoCs. The one thing the new platform won't get, however, is a process node improvement; AMD is building Strix Point on a 4nm node, just like Phoenix/Hawk Point before it.

For this morning's announcement, AMD has unveiled the first two Ryzen AI 300 SKUs designed for notebooks. The first of these is the Ryzen AI 9 HX 370, which features 12 Zen 5 cores with a maximum boost frequency of up to 5.1 GHz, and comes equipped with 36 MB cache (12 MB L2 + 24 MB L3). The other chip to be announced is the Ryzen AI 9 365, which has two fewer Zen 5 cores (10 cores) and operates with a 5,0 GHz boost frequency and a 10 MB L2 + 24 MB L3 cache allocation.

The AMD Computex 2024 Keynote Live Blog (6:30pm PT/02:30 UTC)

Published: Jun 2nd 2024 9:15am on AnandTech

Computex keynote season is kicking into high gear this morning with the show's leading keynote, which is being delivered by AMD. Company CEO Dr. Lisa Su will be presenting a keynote entitled “The future of high-performance computing in the AI era,” and with a run time of 90 minutes, we're expecting AMD to have a whole host of product announcements covering their full spectrum of product categories.

The big expectation here is fresh news around AMD’s Zen 5 CPU core architecture, and the chips built around it. AMD’s most recent Zen 5 roadmap has it slated to deliver all three flavors of Zen 5 by the end of this year, and we’re coming up on the two-year anniversary of the Zen 4 architecture launch.

Along with client chips, AMD has been pushing their server CPUs hard, and they’ve previously told investors that the next-gen EPYC Turin CPU is “looking great”. So we’ll likely hear about both client and server Zen 5 product plans during this keynote.

On the GPU/accelerator side of matters, AMD is mid-cycle (at best) with their Instinct MI300 series accelerators. With the company’s sales repeatedly beating their own expectations, AMD doesn’t seem to need much help moving this premium silicon right now. But with AI being the operative buzzword of this year’s Computex (and indeed, the computing industry as a whole), it would be weird for AMD to not have something to say about their rapidly growing AI accelerator product line.

Come join us at 6:30pm PT / 9:30pm ET / 02:30 UTC to get all the details.

Computex 2024 Keynote Preview: The Great PC Powers Aligned

Published: May 31nd 2024 8:00am on AnandTech

The annual Computex computer expo kicks off in Taepei this weekend. And this year’s show is shaping up to be the most packed in years.

Computex rivals CES for the most important PC trade show of the year, and in most years is attended by not only the numerous local Taiwanese firms (Asus, MSI, ASRock, and others), but the major chip developers have been increasing their own presence as well. These days, while CES itself tends to land more high-profile announcements, in recent years it’s been Computex that has delivered on more substantial announcements. This is largely because tech firms have aligned their product schedules to roll out near gear in the second half of the year, when retail sales are stronger due to the back-to-school and holiday shopping periods.

This year’s show, in turn, is looking to be an especially big year for the PC ecosystem. All the major PC chip firms – AMD, Intel, NVIDIA, and the 4th Musketeer, Qualcomm – are holding keynote addresses at this year’s show, where they’re expected to announce new slates of PC products to ship later this year. In a normal year there is typically only major announcements from one or two of the major chip firms, so having all four of them at the show delivering lengthy keynotes is setting things up for what should be an exceptional show.

TSMC's 3D Stacked SoIC Packaging Making Quick Progress, Eyeing Ultra-Dense 3μm Pitch In 2027

Published: May 31nd 2024 11:00am on AnandTech

TSMC's 3D-stacked system-on-integrated chips (SoIC) advanced packaging technologies is set to evolve rapidly. In a presentation at the company's recent technology symposium, TSMC outlined a roadmap that will take the technology from a current bump pitch of 9μm all the way down to a 3μm pitch by 2027, stacking together combinations of A16 and N2 dies.

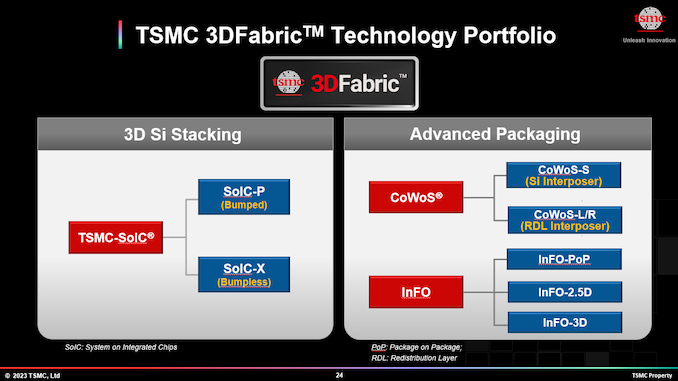

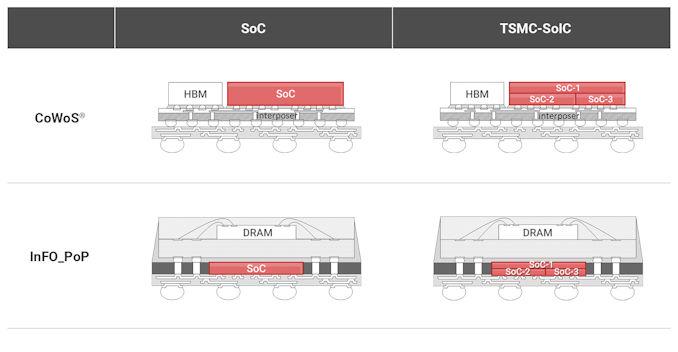

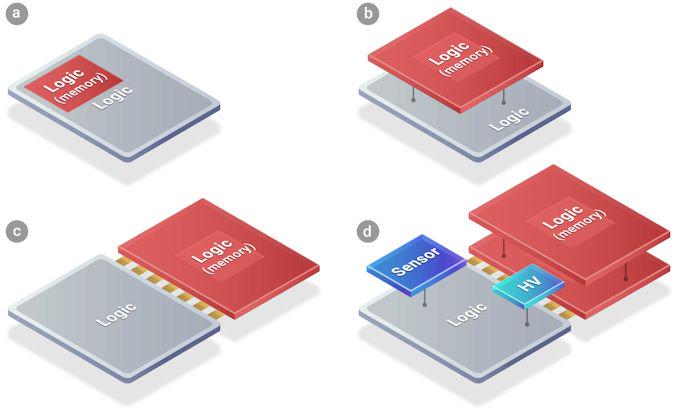

TSMC has a number of advanced packaging technologies, including 2.5D CoWoS and 2.5D/3D InFO. Perhaps the most intriguing (and complex) method is their 3D-stacked system-on-integrated chips (SoIC) technology, which is TSMC's implementation of hybrid wafer bonding. Hybrid bonding allows two advanced logic devices to be stacked directly on top of each other, allowing for ultra-dense (and ultra-short) connections between the two chips, and is primarily aimed at high performance parts. For now, SoIC-X (bumpless) is used for select applications, such as AMD's 3D V-cache technology for CPUs, as well as their Instinct MI300-series AI products. And while adoption is growing, the current generation of the technology is constrained by limitations on die sizes and interconnection pitches.

But those limitations are expected to give way quickly, if all goes according to plan for TSMC. SoIC-X technology is going to advance fast, and by 2027, it will be possible assemble a chip pairing a reticle-sized top die made on TSMC's leading-edge A16 (1.6nm-class) on a bottom die produced using TSMC's N2 (2nm-class). These dies, in turn, would be connected using 3μm bond pitche ssilicon vias (TSVs), three times the density of the size of today's 9μm pitch. Such small interconnections will allow for a much larger number of connections overall, greatly increasing the bandwidth density (and thus performance) of the assembled chip.

TSMC's SoIC-X Roadmap Data by TSMC (Compiled by AnandTech) 2022 2023 2024 2025 2026 2027 Top Die N7 N5 N4 N4 N2 A16 Bottom Die N7 ≥N6 ≥N5 ≥N4 ≥N3 ≥N2 Bond Pitch 9 μm 9 μm 6 μm 6 μm 4.5 μm 3 μm Size* 0.1 reticle 0.4 reticle 0.8 reticle 1 reticle 1 reticle 1 reticle*TSMC considers reticle size as roughly 830 mm2.

Improved hybrid bonding techniques are intended to allow TSMC's big HPC customers – AMD, Broadcom, Intel, NVIDIA, and the like – to build large, ultra-dense disaggregated processor designs for demanding applications, where distance between the dies is critical, as is the overall floor space used. Meanwhile, for applications where only performance matters, it will be possible to place multiple SoIC-X packages on a CoWoS interposer to get improved performance at a lower power consumption.

In addition to developing its bumpless SoIC-X packaging technology aimed at devices that require extreme performance, TSMC will also launch its bumped SoIC-P packaging process in the near future. SoIC-P is designed for cheaper lower performance applications that still want 3D-stacking, but don't need the additional performance and complexity that comes with bumpless copper-to-copper TSV connections. This packing technique will enable a broader range of companies to leverage SoIC, and while TSMC can't speak for their customers' plans, a cheaper version of the technology may make it accessible for more cost-conscious consumer applications.

Per TSMC's current plans, by 2025 the company will offer a face-to-back (F2B) bumped SoIC-P technology capable of pairing a 0.2-reticle sized N3 (3nm-class) top die with an N4 (4nm-class) bottom die, which will be connected using 25μm pitch microbumps (µbumps). In 2027, TSMC will introduce bumped face-to-face (F2F) SoIC-P technology, which will be able to place an N2 top die on an N3 bottom die with a pitch of 16μm.

TSMC's SoIC-P Roadmap Data by TSMC (Compiled by AnandTech) 2025 2027 Top Die N3 N2 Bottom Die ≥N4 ≥N3 Bond Pitch 25 μm 16 μm Size* 0.2 reticle 0.4 reticle Die Orientation face-to-back face-to-face Qualification Time Q4 2024 for mobile SoC Q2 2026 for HPC*TSMC considers reticle size as roughly 830 mm2

A lot of work has to be done to make SoIC more popular and accessible among chip developers, including continuing to iprove their die-to-die interfaces. But TSMC seems to be very optimistic about SoIC adoption by the industry, and expects around 30 SoIC designs to be released by 2026 – 2027.

GEEKOM A7 mini-PC Review : Premium Phoenix in a Compact 4x4 Package

Published: May 31nd 2024 8:00am on AnandTech

The introduction of the Intel NUC in the early 2010s kickstarted the ultra-compact form-factor (UCFF) trend for desktop systems. Processors with TDPs ranging from 6 - 15W formed the backbone of this segment in the initial years. The emergence of configurable TDPs for notebook processors has prompted some vendors to introduce UCFF systems with regular 45W TDP processors (albeit, in cTDP-down mode).

GEEKOM, the private label brand of Shenzhen Jiteng Network Technology Co., has emerged as a popular UCFF system vendor in the last couple of years. After starting off with systems based on older processors, the company has moved on to introducing units carrying the latest and greatest from both AMD and Intel. The company has also been innovating on the form-factor side with compact boards smaller than the traditional 4"x4" ones in the NUC clones. The GEEKOM A7 is one such system based on AMD's Phoenix lineup.

The system is available in two configurations - one with the Ryzen 7 7840HS, and the other with the Ryzen 9 7940HS. The company sent over the flagship configuration to put through our evaluation routine for small form-factor computing systems. Read on to explore the performance profile and value proposition of the system, along with a discussion of the trade-offs involved in cramming a powerful notebook processor inside a system smaller than the traditional NUC.