The Enermax Revolution D.F. 12 750W ATX 3.1 PSU Review: Compact Contender

Published: Jun 7nd 2024 8:00am on AnandTech

Enermax, established in 1990, is a renowned Taiwanese company in the PC hardware industry, particularly recognized for its innovative power supply units (PSUs), cooling solutions, and PC cases. Over the years, Enermax has built a reputation for engineering reliable, high-performance PSUs that primarily target enthusiasts and professional users. Their commitment to quality and technological advancement has kept them at the forefront of the industry, constantly evolving to meet the demands of the ever-changing tech landscape.

In this review, we are looking at the latest addition to Enermax's impressive PSU lineup: the Revolution D.F. 12 750W PSU. This is the second ATX 3.1-compliant power supply to arrive in our labs, and, broadly speaking, illustrates how we're approaching the inflection point for PSU vendors to update their designs for Intel's revised PSU standard.

As for the Revolution D.F. 12 itself, Enermax's new PSU pursues a balanced design, meeting modern gaming PCs mid-way with good conversion efficiency and an overall robust power delivery system. With features like fully modular cables with per-wire sleeving, a dynamic hybrid fan control for optimal cooling, and advanced topologies, the Revolution D.F. 12 750W is primed to deliver on both reliability and performance. We will delve into its specifications, build quality, and performance metrics to see if the new unit lives up to Enermax's esteemed legacy.

Micron's GDDR7 Chip Smiles for the Camera as Micron Aims to Seize Larger Share of HBM Market

Published: Jun 7nd 2024 7:00am on AnandTech

For Computex week, Micron was at the show in force in order to talk about its latest products across the memory spectrum. The biggest news for the memory company was that it has kicked-off sampling of it's next-gen GDDR7 memory, which is expected to start showing up in finished products later this year and was being demoed on the show floor. Meanwhile, the company is also eyeing taking a much larger piece of the other pillar of the high-performance memory market – High Bandwidth Memory – with aims of capturing around 25% of the premium HBM market.

GDDR7 to Hit the Market Later This YearMicron's first GDDR7 chip is a 16 Gb memory device with a 32 GT/sec (32Gbps/pin) transfer rate, which is significantly faster than contemporary GDDR6/GDDR6X. As outlined with JEDEC's announcement of GDDR7 earlier this year, the latest iteration of the high-performance memory technology is slated to improve on both memory bandwidth and capacity, with bandwidths starting at 32 GT/sec and potentially climbing another 50% higher to 48 GT/sec by the time the technology reaches its apex. And while the first chips are starting off at the same 2GByte (16Gbit) capacity as today's GDDR6(X) chips, the standard itself defines capacities as high as 64Gbit.

Of particular note, GDDR7 brings with it the switch to PAM3 (3-state) signal encoding, moving from the industry's long-held NRZ (2-state) signaling. As Micron was responsible for the bespoke GDDR6X technology, which was the first major DRAM spec to use PAM signaling (in its case, 4-state PAM4), Micron reckons they have a leg-up with GDDR7 development, as they're already familiar with working with PAM.

The GDDR7 transition also brings with it a change in how chips are organized, with the standard 32-bit wide chip now split up into four 8-bit sub-channels. And, like most other contemporary memory standards, GDDR7 is adding on-die ECC support to hold the line on chip reliability (though as always, we should note that on-die ECC isn't meant to be a replacement for full, multi-chip ECC). The standard also implements some other RAS features such as error checking and scrubbing, which although are not germane to gaming, will be a big deal for compute/AI use cases.

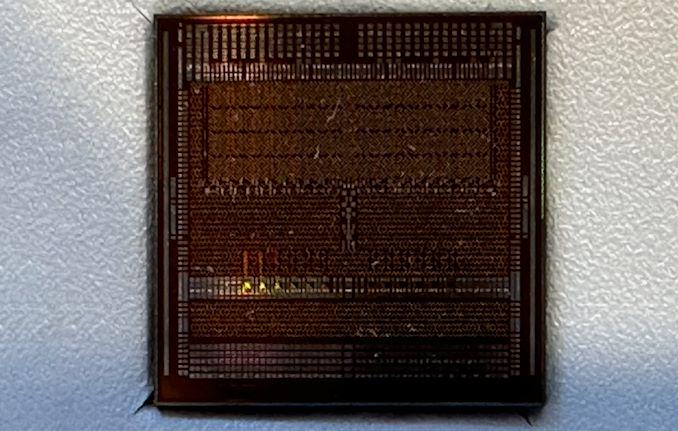

The added complexity of GDDR7 means that the pin count is once again increasing as well, with the new standard adding a further 86 pins to accommodate the data transfer and power delivery changes, bringing it to a total of 266 pins. With that said, the actual package size is remaining unchanged from GDDR5/GDDR6, maintaining that familiar 14mm x 12mm package. Memory manufacturers are instead using smaller diameter balls, as well as decreasing the pitch between the individual solder balls – going from GDDR6's 0.75mm x 0.75mm pitch to a slightly shorter 0.75mm x 0.73mm pitch. This allows the same package to fit in another 5 rows of contacts.

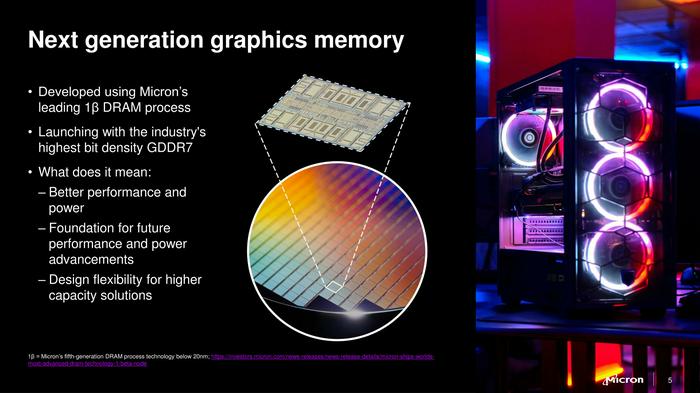

As for Micron's own production plans, the company is using its latest 1-beta (1β) fabrication process. While the major memory manufacturers don't readily publish the physical parameters of their processes these days, Micron believes that they have the edge on density with 1β, and consequently will be producing the densest GDDR7 at launch. And, while more nebulous, the company company believes that 1β will give them an edge in power efficiency as well.

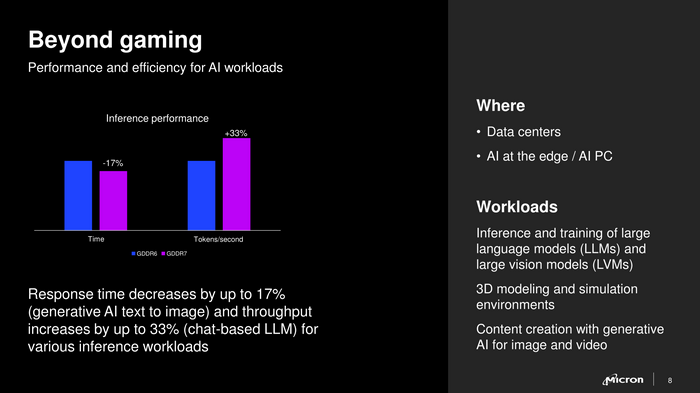

Micron says that the first devices incorporating GDDR7 will be available this year. And while video card vendors remain a major consumer of GDDR memory, in 2024 the AI accelerator market should not be overlooked. With AI accelerators still bottlenecked by memory capacity and bandwidth, GDDR7 is expected to pair very well with inference accelerators, which need a more cost-effective option than HBM.

Micron Hopes to Get to Mid-20% HBM Market Share with HBM3ESpeaking of HBM, Micron was the first company to formally announce its HBM3E memory last year, and it was among the first to start its volume shipments earlier this year. For now, Micron commands a 'mid-single digit' share of this lucrative market, but the company has said that it plans to rapidly gain share. If all goes well, by the middle of its fiscal 2025 (i.e., the end of calendar Q1 2025) the company hopes to capture a mid-20% share of the HBM market.

"As we go into fiscal year 2025, we expect our share of HBM to be very similar to our overall share on general DRAM market," said Praveen Vaidyanathan, vice president and general manager of the Compute Products Group at Micron. "So, I would say mid-20%. […] We believe we have a very strong product as [we see] a lot of interest from various GPU and ASIC vendors, and continuing to engage with customers […] for the next, say 12 to 15 months."

When asked whether Micron can accelerate output of HBM3E at such a rapid pace in terms of manufacturing capacity, Vaidyanathan responded that the company has a roadmap for capacity expansion and that the company would meet the demand for its HBM3E products.

Gallery: Micron GDDR7 Press Deck

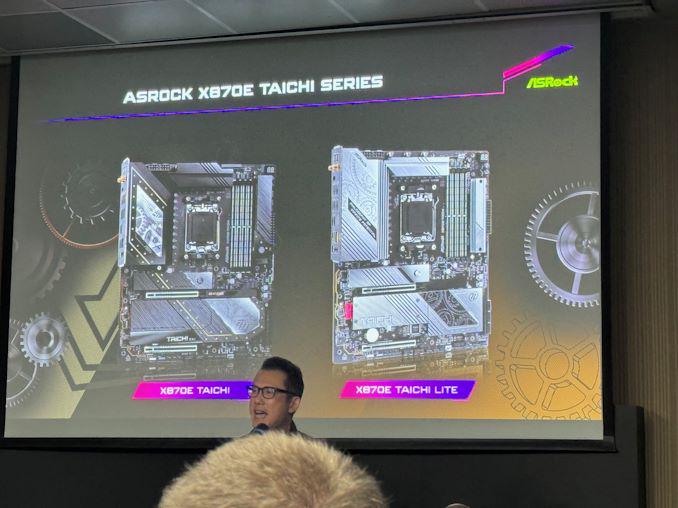

ASRock Unveils Motherboards For Ryzen 9000 At Computex 2024: X870E Taichi and X870E Taichi Lite

Published: Jun 6nd 2024 10:20am on AnandTech

During Computex 2024, ASRock held an event to unveil some of its upcoming X870E motherboards, designed for AMD's Zen 5-based Ryzen 9000 series processors. ASRock's announcement includes a pair of Taichi-branded boards, the X870E Taichi and the lighter X870E Taichi lite, which uses AMD's Promontory 21 chipset for AM5.

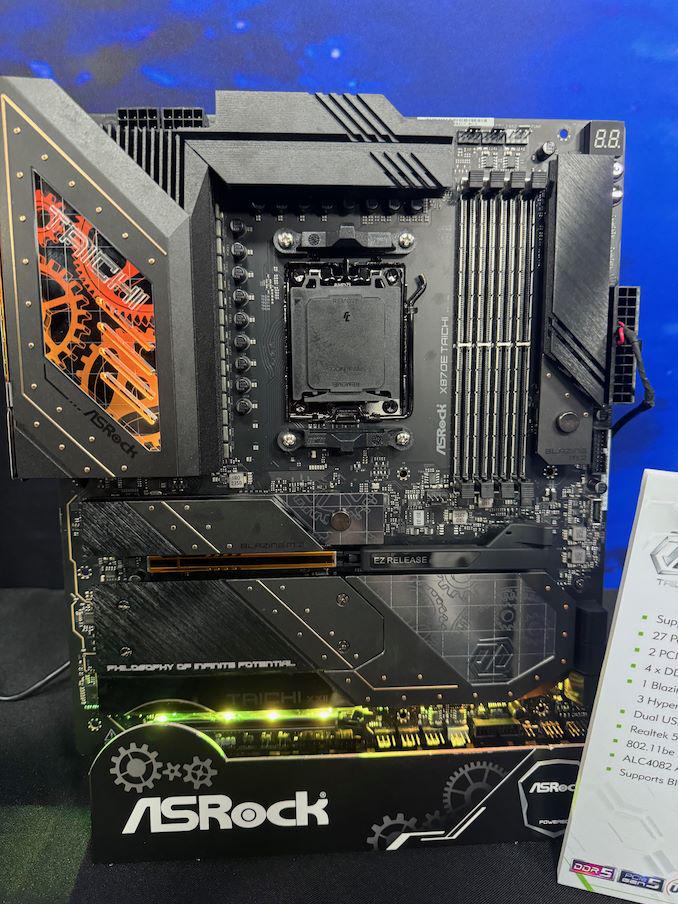

The current flagship model announced from ASRock's X870E line-up for Ryzen 9000 is the ASRock X870E Taichi. ASRock is advertising a large 27-phase power delivery through 110A SPS, suggesting this board is designed for overclockers and all-around power users. Two PCIe 5.0 x16 slots provide high-speed bandwidth for cutting-edge graphics cards and other devices. The four DDR5 DIMM slots allow users to experience the most advanced memory technology for faster and more powerful configurations.

The storage offering is impressive, with three Hyper M.2 slots supporting PCIe Gen5 x4. Also present are two USB4 Type-C ports that deliver expansive and high-bandwidth connectivity with solid networking capabilities, including a Realtek 5 GbE LAN and Wi-Fi 7 CNVi. The audio setup includes a Realtek ALC4082 codec and ESS SABRE9218 DAC supporting high-fidelity sound. The BIOS flashback feature is also a nice touch, and we believe this should be a feature on all mid-range to high-end motherboards, which provides an easy way to update the firmware without installing a CPU. The X870E Taichi is a premium motherboard with a slew of features to help attain superior performance and be future-proof for emerging technologies.

The ASRock X870E Taichi Lite offers a streamlined alternative to the X870E Taichi, retaining key features like the 27-phase power delivery with 110A smart power stages, dual PCIe 5.0 x16 slots operating at x16 or x8/x8, four DDR5 DIMM slots, and three Hyper M.2 slots (PCIe Gen5 x4). It includes Realtek 5GbE LAN, Wi-Fi 7, and the ALC4082 codec with ESS SABRE9218 DAC for high-quality audio as the more premium Taichi; the Taichi Lite features a simpler silver-themed design, while the standard Taichi has a more intricate gold-accented and fanciful aesthetics.

In terms of availability, there's no actual release date, and according to Andreas Schilling from HawrdwareLUXX, the X870E and X870 motherboards aren't expected to be launched at the same time as the Ryzen 9000 series featuring Zen 5 cores. We will investigate this and contact the motherboard vendors to confirm the situation. Still, as X870E/X870 barely differ from the current X670E/X670 motherboards, and as they are all AM5 socketed, users can use these with Ryzen 9000 processors when they launch.

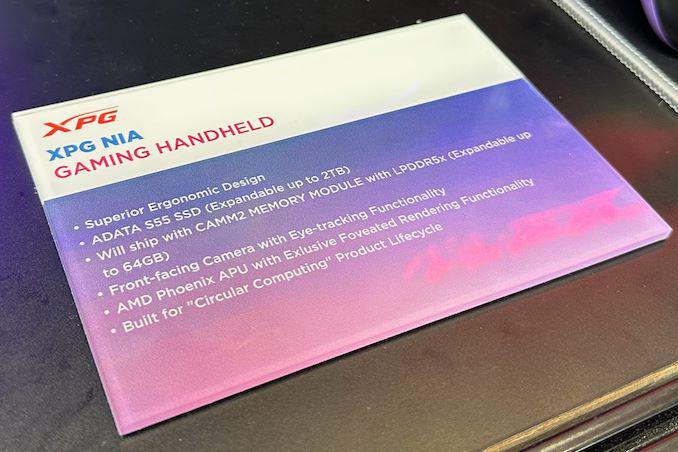

XPG Demos "Nia" Handheld Gaming PC With Foveated Rendering, Swappable DRAM

Published: Jun 5nd 2024 12:00am on AnandTech

With the rise of the handheld gaming PC market, we've seen PC vendors and their partners toy with a number of tricks and tweaks to improve improve framerates in games, with some of their latest efforts on display at this year's Computex trade show. Perhaps the most interesting find thus far comes from ADATA sub-brand XPG, who is demoing their prototype "Nia" handheld PC, which uses eye tracking and dynamic foveated rendering to further improve their rendering performance.

For those unfamiliar, dynamic foveated rendering is a graphics technique that is sometimes used to boost performance in virtual reality (VR) and augmented reality (AR) applications by taking advantage of how human vision works. Typically, humans can only perceive detailed imagery in the relatively small central area of our vision called the fovea, while our peripheral vision is much less detailed. Dynamic foveated rendering, in turn, exploits this by using real-time eye tracking to determine where the user is looking, and then rendering just that area in high/full resolution, while rendering the peripheral areas in lower resolution. The net result is that only a fraction of the screen is rendered at full detail, which cuts down on the total amount of rendering work required and boosting framerates on performance-limited devices.

As stated before, this technology is sometimes used in high-end AR/VR headsets, where high resolution displays are placed mere inches from one's face. This ends up being an ideal use case for the technique, since at those distances, only a small fraction of the screen is within the fovea.

Using dynamic foveated rendering for a handheld, on the other hand, is a more novel application. All of the same visual principles apply, but the resolutions at play are lower, and the screen is farther from the users' eyes. This makes a handheld device a less ideal use case, at least on paper, as a larger portion of the screen is going to be in the fovea, and thus will need to be rendered at full resolution. None the less, it will be interesting to see how XPG's efforts pan out, and if dynamic foveated rendering is beneficial enough for handheld PCs. As we sometimes see with trade show demos, not everything makes it out of the prototype stage.

According to a press release put out by ADATA ahead of the trade show, the eye tracking technology is being provided by AMD collaborator Eyeware. Notably, their software-based approach runs on top of standard webcams, rather than requiring IR cameras. So the camera hardware itself should be pretty straight-forward.

Foveated rendering aside, XPG is making sure that the Nia won't be a one-trick pony. The handheld's other major claim to fame is its hardware swappability. The prototype handheld not only features a removable M.2-2230 SSD, but the company is also taking advantage of the recently-introduced LPCAMM2 memory module standard to introduce removable DRAM. Via a hatch in the back of the handheld, device owners would be able to swap out LPCAMM2 LPDDR5X modules for higher capacity versions. This would give the handheld an additional degree of future-proofness over current handhelds, which use non-replaceable soldered-down memory.

Rounding out the package, the current prototype is based on an AMD's Zen 4 Phoenix APU, which is used across both of the company's current mobile lines (Ryzen Mobile 7000/8000 and Ryzen Z1). Meanwhile, the unit's display is adjustable, allowing it to be angled away from the body of the handheld.

Assuming all goes well with the prototype, XPG aims to release a finished product in 2025.

G.Skill Demonstrates DDR5-10600 Memory Modules On Ryzen 8500G System

Published: Jun 5nd 2024 10:30am on AnandTech

Ultra-high performance memory modules are a staple of of Computex, and it looks like this year G.Skill is showing off the highest performance dual-channel memory module kit to date. The company is demonstrating a DDR5 kit capable of 10,600 MT/s data transfer rate, which is a considerably higher speed compared to memory modules available today.

The dual-channel kit that G.Skill is demonstrating is a 32 GB Trident Z5 RGB kit that uses cherry-picked DDR5 memory devices and which can work in a DDR5-10600 mode with CL56 62-62-126 timings at voltages that are way higher than standard. The demoed DIMMs are running the whole day in a fairly warm room, though it does not really run demanding applications or stress tests.

Traditionally, memory module makers like G.Skill use Intel processors to demonstrate their highest-performing kits. But with the DDR5-10600 kit, the company uses AMD's Ryzen 5 8500G processor, which is a monolithic Zen 4-based APU with integrated graphics that's normally sold for budget systems. The motherboard is a high-end Asus ROG Crosshair X670E Gene and the APU is cooled down using a custom liquid cooling system The Asus ROG Crosshair X670E Gene motherboard has only two memory slots, which greatly helps to enable high data transfer rates, so it is a very good fit for the DDR5-10600 dual-channel kit.

Though I have sincere doubts that someone is going to use an ultra-expensive DDR5-10600 memory kit and related gate with this inexpensive processor, it is interesting (and unexpected) to see an AMD APU as a good fit to demonstrate performance potential of G.Skill's upcoming modules.

Speaking of availability of G.Skill's DDR5-10600 memory, it does not look like this kit is around the corner. The fastest DDR5 kit that G.Skill has today is its DDR5-8400 offering, so the DDR5-10600 will come to market a few speed bins later as G.Skill certainly needs to test the kit with various CPUs and ensure its stability.

One other thing to keep in mind is that both AMD and Intel are about to release new desktop processors this year, with the Ryzen 9000-series and Arrow Lake processors respectively. So G.Skill will undoubtedly focus on tuning its DDR5-10600 and other high-end kits primarily with those new CPUs.

Update on Intel's Panther Lake at Computex 2024, Intel Powering Up Intel 18A Wafer Next Week

Published: Jun 4nd 2024 11:00am on AnandTech

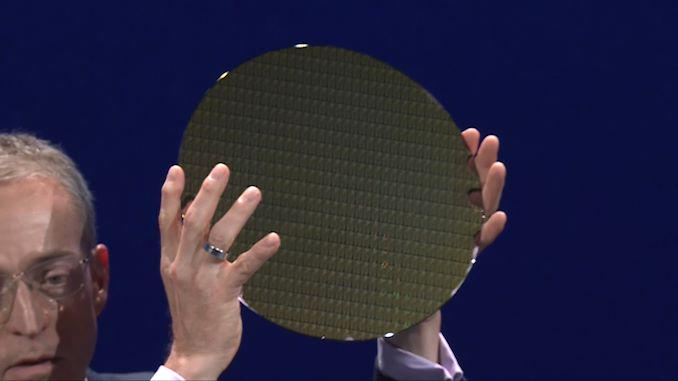

During the Intel keynote hosted by CEO Pat Gelsinger, he gave the world a glimpse into the Intel Client roadmap until 2026. Meteor Lake launched last year on that roadmap, and Lunar Lake, which we dived into yesterday as Intel disclosed technical details about the upcoming platform. Pat also presented a wafer on stage, Panther Lake, and he gave some additional information about Intel's forthcoming Panther Lake platform, which is expected in 2025.

We covered Intel's initial announcement about the Panther Lake platform last year. It is set to be Intel's first client platform using its Intel 18A node. Aside from once again affirming that things are on track for a 2026 launch, Pat Gelsinger, Intel's CEO, also confirmed that they will be powering on the first 18A wafer for Panther Lake as early as next week.

One element to consider from last year is that Lunar Lake, which was expected to be built on the Intel 20A node, is built using TSMC, with the Lunar Lake compute tile with Xe2-LPG graphics on TSMC N3B, and the I/O tile on TSMC N6. Pat confirmed on stage that Panther Lake will be on Intel 18A. Still, he didn't divulge which P and E cores it would use or if it would use a different variant of the incoming Lion Cove P-cores and Skymont E-Cores, which is coming with Lunar Lake SoCs, while the same cores will be used in Arrow Lake for desktop expected this year.

As we head into the second half of 2024 and after Lunar Lake launches, Intel may divulge more information, including the architectural advancements Panther Lake is expected to bring. Until then, we will have to wait and see.

Frore Demos Solid-State AirJet Cooler in Action: Significantly Improving Both Laptop and SSD Performance

Published: Jun 4nd 2024 6:00am on AnandTech

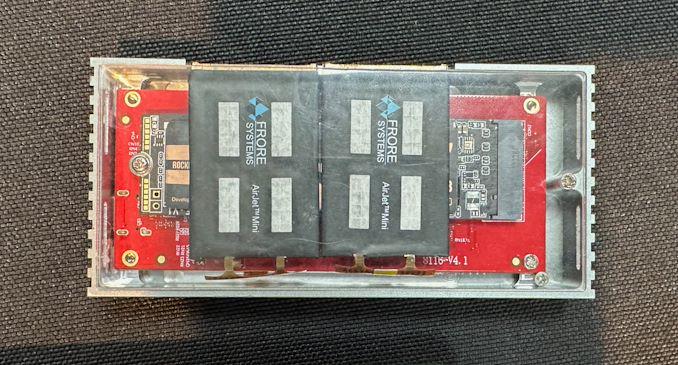

In recent months, Frore Systems has been turning heads with their fanless solid-state air cooler technology. The AirJet, as it's come to be called, was previously shown off at CES this year; and for Computex, the company is back with a fresh round of demonstrations.

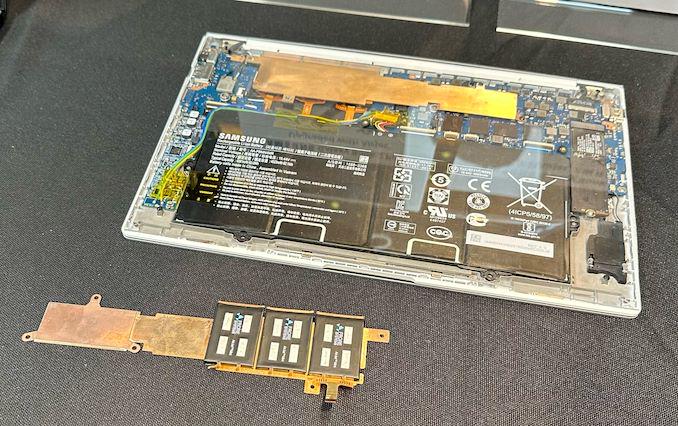

For the show, Frore has a number of demonstrations running in a fairly large showroom. The company is looking to address a wide range of products, from tablets to notebooks to small PCs, as well as embedded tablets. But there were two showcases in particular that caught my immediate attention: a Samsung Galaxy Book with and without Frore's AirJet, and an 8 TB Sabrent SSD in an external enclosure.

The Samsung Galaxy Book 2 Pro is an ultra-thin notebook that is normally cooled by a fan that, as argued by Flore, does not do its job properly. According to the company, the stock laptop only has enough cooling capacity to sustain 12W heat/power before it hits Tmax, whereas a retrofitted version with Frore's AirJet installed allows it to hold steady-state operation at 16W – and consequently delivering higher performance. In terms of Cinebench R23 multi-threaded results, we are talking about 5330 points for the modded notebook, versus 4255 for the off-the-shelf Galaxy Book 2 Pro.

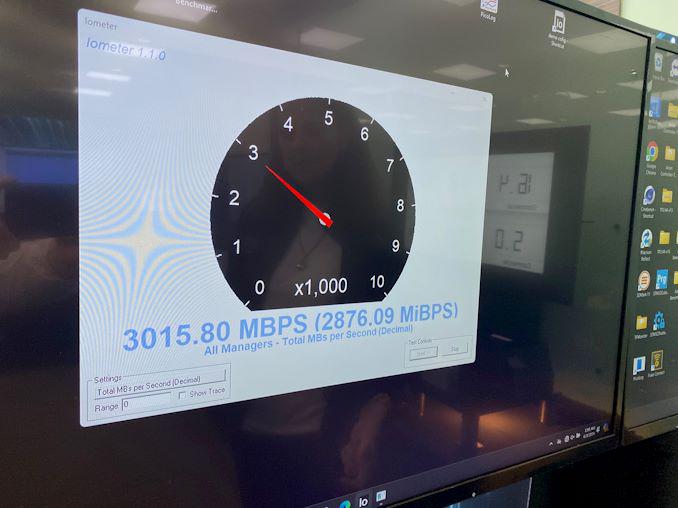

The potential use cases for Frore Systems's AirJet solid-state cooling technology do not end with CPUs, either. As mentioned previously, the company is also demonstrating the AirJet Mini on Sabrent 8TB SSDs in Orico external enclosures, showcasing the advantage of the silent active cooler over passive cooling. The passively-cooled drive reached 62°C and leveled out at 1,320 MB/s due to thermal throttling. In contrast, the AirJet-cooled drive maintained a temperature of 42°C and achieved a considerably higher performance of 3,016 MB/s.

According to Frore, this significant improvement in both temperature and performance has already led to one major external SSD vendor adopting AirJet technology to improve the performance of their drives. Unfortunately, Frore isn't naming any names, only stating that it's a "big name."

Now, Frore's AirJet Mini and Mini Slim coolers can dissipate up to 5W of power each, and can be combined in to larger blocks of up to 5 coolers (we are talking about announced solutions, technologically scaling could he higher, but this is an entirely different conversation). So the technology does have some scalability limitations that makes it best-suited for lower-power devices. None the less, removing 25W of thermal energy from a modern laptop without a fan can make a huge difference in the performance of these normally passively-cooled devices.

Of course, the main goal for these Computex demos is far more than just showing off AirJets to the public; what Frore would really like to do is to land a deal for its solid-state cooling solution with a major PC vendor (e.g., Apple, Samsung, etc.). Though to do that, Frore has to pass qualification tests and ensure availability of its products, which is something the company says it's currently working on. Meanwhile, from performance point of view, especially given their dimensions, AirJets look very impressive.

Intel Unveils Lunar Lake Architecture: New P and E cores, Xe2-LPG Graphics, New NPU 4 Brings More AI Performance

Published: Jun 3nd 2024 11:00am on AnandTech

Intel this morning is lifting the lid on some of the finer architectural and technical details about its upcoming Lunar Lake SoC – the chip that will be the next generation of Core Ultra mobile processors. Once again holding one of their increasingly regular Tech Tour events for media and analysts, Intel this time set up shop in Taipei just before the beginning of Computex 2024. During the Tech Tour, Intel disclosed numerous facets of Lunar Lake, including their new P-Core design codenamed Lion Cove and a new wave of E-cores that are a bit more like Meteor Lake's pioneering Low Power Island E-Cores. Also disclosed was the Intel NPU 4, which Intel claims delivers up to 48 TOPS, surpassing Microsoft's Copilot+ requirements for the new age of AI PCs.

Intel's Lunar Lake represents a strategic evolution in their mobile SoC lineup, building on their Meteor Lake launch last year, focusing on enhancing power efficiency and optimizing performance across the board. Lunar Lake dynamically allocates tasks to efficient cores (E-cores) or performance cores (P-cores) based on workload demands by leveraging advanced scheduling mechanisms, which are assigned to ensure optimal power usage and performance. Still, once again, Intel Thread Director, along with Windows 11, plays a pivotal role in this process, guiding the OS scheduler to make real-time adjustments that balance efficiency with computational power depending on the intensity of the workload.

The Intel Computex 2024 Keynote Live Blog (8:00pm PT/03:00 UTC)

Published: Jun 3nd 2024 10:00am on AnandTech

Closing out the last of the major PC-focused keynotes at Computex 2024 this evening, we have Intel. The long-reigning leader of the PC CPU market, Intel is in the middle of executing its plans to get back on track on both the manufacturing and chip design aspects of the business. Tonight’s keynote, being helmed by the highly-animated Pat Gelsinger, is titled “Bringing AI Everywhere.” And, like so many other Computex presentations and announcements this week, AI hardware is going to play a big part, as Intel outlines a full stack of products for client and server computing.

Of the four great PC chip vendors at the show, Intel has been the most up-front about what to expect from their hour-long presentation. The company’s Computex 2024 page already outlines their four major topics: AI PCs, Xeon 6 Processors, Gaudi AI accelerators, and Intel’s OpenVINO software ecosystem.

On the consumer hardware front, the company set the table with a significant teaser earlier this month about their forthcoming mobile PC SoC, Lunar Lake. The next generation of Core Ultra processors, Intel is touting significant energy efficiency gains for the mobile-focused chip, with new architectures driving their Performance and Efficiency CPU cores, Xe2 GPU, and a much faster 45+ TOPS (INT8) NPU. While the Lunar Lake announcement is coming relatively soon after the Meteor Lake launch, Intel has made it clear that it’s not going to hold back on shipping future products; they are looking to make up for lost time. Still, Lunar Lake devices are not expected to hit retail shelves until Q4 of this year, so this announcement is coming months in advance of the hardware itself.

On the server front, Intel has been publicly prepping for the launch of a new generation of Xeons with the Xeon 6 platform. The most notable part of this being the release of the company’s first Efficiency-core Xeon, Sierra Forest. Sierra Forest is set to be the first Xeon 6 chip out the door this year, and will offer up to 288 E cores on a single chip, allowing Intel to tap into the many (many) core CPU markets that AMD and Arm-based rivals have been unopposed at thus far.

Finally, the company has fully pivoted its server AI accelerator strategy to its Gaudi accelerators. Gaudi 3 was introduced back in April, and while it isn’t expected to go toe-to-toe with NVIDIA’s top accelerators in every workload, Intel is betting that they can beat NVIDIA on critical workloads, all while undercutting them significantly in pricing. The first Gaudi 3 parts are set to be released in the second half of this year, so hopefully we’ll be hearing a bit more about Intel’s plans as part of their keynote.

As always, the AnandTech crew is live and in person to catch this final Computex keynote. So please come join us at 8:00pm PT / 11:00pm ET / 03:00 UTC to get all the details.

AMD Announces Zen 5-based EPYC “Turin” Processors: Up to 192 Cores, Coming in H2’2024

Published: Jun 3nd 2024 1:15am on AnandTech

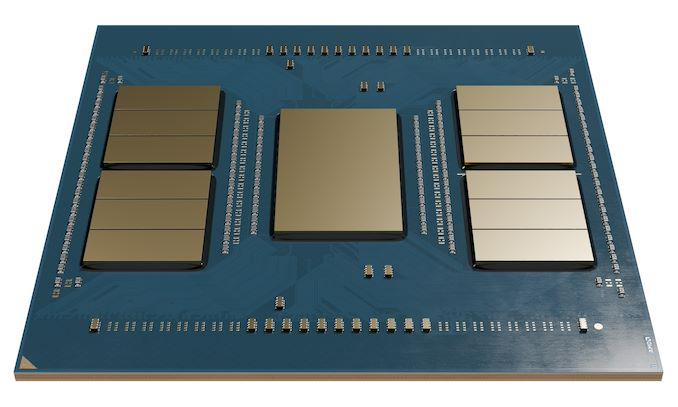

With AMD’s Zen 5 CPU architecture only a month away from its first product releases, the new CPU architecture was placed front and center for AMD’s prime Computex 2024 keynote. Outlining how Zen 5 will lead to improved products across AMD’s entire portfolio, the company laid out their product plans for the full triad: mobile, desktop, and servers. And while server chips will be the last parts to be released, AMD also saved the best for last by showcasing a 192 core EPYC “Turin” chip.

Turin is the catch-all codename for AMD’s Zen 5-based EPYC server processors – what will presumably be the EPYC 9005 series. The company has previously disclosed the name in earnings calls and other investor functions, outlining that the chip was already sampling to customers and that the silicon was “looking great.”

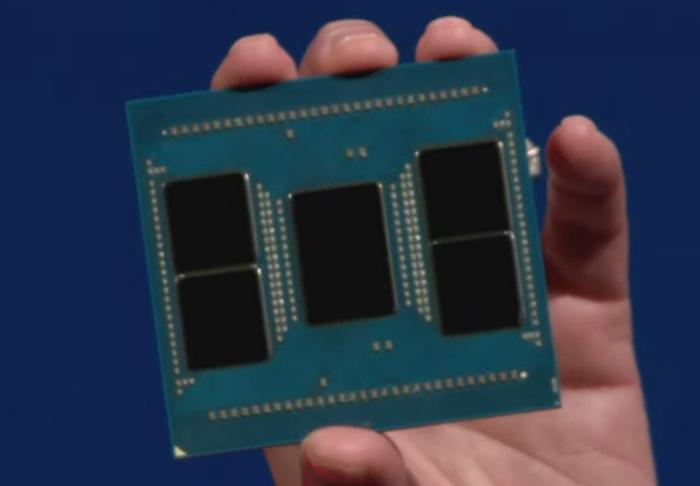

The Computex reveal, in turn, is the first time that the silicon has been shown off to the public. And with it, we’ve received the first official confirmation of the chip’s specifications. With SKUs up to 192 CPU cores, it’s going to be a monster of an x86 CPU.

AMD EPYC CPU Generations AnandTech EPYC 5th Gen (Turin, Z5c) EPYC 9704 (Bergamo) EPYC 9004 (Genoa) EPYC 7003 (Milan) CPU Architecture Zen 5c Zen 4c Zen 4 Zen 3 Max CPU Cores 192 128 96 64 Memory Channels 12 x DDR5 12 x DDR5 12 x DDR5 8 x DDR4 PCIe Lanes 128 x 5.0 128 x 5.0 128 x 5.0 128 x 4.0 L3 Cache ? 256MB 384MB 256MB Max TDP 360W? 360W 400W 280W Socket SP5 SP5 SP5 SP3 Manufacturing Process CCD: TSMC N3 IOD:TSMC N6 CCD: TSMC N5 IOD: TSMC N6 CCD: TSMC N5 IOD: TSMC N6 CCD: TSMC N7 IOD: GloFo 14nm Release Date H2'2024 06/2023 11/2022 03/2021Though only a brief tease, AMD’s Turin showcase did confirm a few, long-suspected details about the platform. AMD will once again be using their socket SP5 platform for Turin processors, which means the chips are drop-in compatible with EPYC 9004 Genoa (and Bergamo). The reuse of SP5 means that customers and server vendors can immediately swap out chips without having to build/deploy whole new systems. It also means that Turin will have the same base memory and I/O options as the EPYC 9004 series: 12 channels of DDR5 memory, and 128 PCIe 5.0 lanes.

In terms of power consumption, existing SP5 processors top out at 400 Watts, and we’d expect the same for these new, socket-compatible chips.

As for the Turin chip itself, while AMD is not going into further detail on its configuration, all signs point to this being a Zen 5c configuration – that is, built using CCDs designed around AMD’s compact Zen 5 core configuration. This would make the Turin chip on display the successor to Bergamo (EPYC 9704), which was AMD’s first compact core server processor, using Zen 4c cores. AMD’s compact CPU cores generally trade off per-core performance in favor of allowing more CPU cores overall, with lower clockspeed limits (by design) and less cache memory throughout the chip.

According to AMD, the CCDs on this chip were fabbed on a 3nm process (undoubtedly TSMC’s), with AMD apparently looking to take advantage of the densest process available in order to maximize the number of CPU cores the can place on a single chip. Even then, the CCDs featured here are quite sizable, and while we’re waiting for official die size numbers, it would come as no surprise if Zen 5’s higher transistor count more than offset the space savings of moving to 3nm. Still, AMD has been able to squeeze 12 CCDs on to the chip – 4 more than Bergamo – which is what’s allowing them to offer 192 CPU cores instead of 128 as in the last generation.

Meanwhile, the IOD is confirmed to be produced on 6nm. Judging from that fact, the pictures, and what AMD’s doing with their Zen 5 desktop products, there is a very good chance that AMD is using either the same or a very similar IOD as on Genoa/Bergamo. Which goes hand-in-hand with the socket/platform at the other end of the chip staying the same.

AMD’s brief teaser did not discuss at all any other Turin configurations. So there is nothing else official to share about Turin chips built using full-sized Zen 5 CPU cores. With that said, we know that the full-fat cores going into the Ryzen 9000 desktop series pack 8 cores to a CCD and are being fabbed on a 4nm process – not 3nm – so that strongly implies that EPYC Zen 5 CCDs will be the same. Which, if that pans out, means that Turin chips using high performance cores will max out at 96 cores, the same as Genoa.

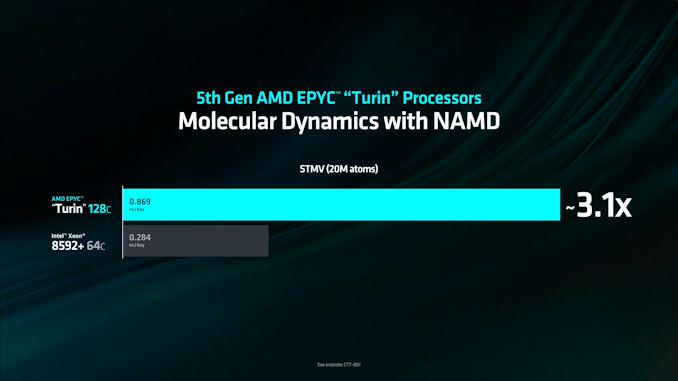

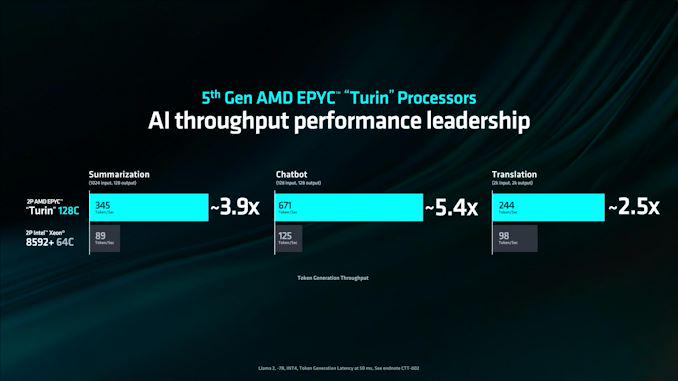

Hardware configurations aside, AMD also showcased a couple of benchmarks, pitting the new EPYC chips against Intel’s Xeons. As you’d expect in a keynote teaser, AMD was winning handily. Though it is interesting to note that the chips benchmarked were all 128 core Turins – which means those benchmarks may have been on chips using the full-fat cores.

AMD will be shipping EPYC Turin in the second half of this year. More details on the chips and configurations will follow once AMD gets closer to the EPYC launch.